Enterprise FPGA prototyping is being used to fill the gap between an emulator’s powerful analysis/debug capabilities and the raw performance of a desktop FPGA prototyping board.

System-on-chip (SoC) designers are tasked with completing full system-level verification before mask production. This means thoroughly testing hardware blocks, interactions between those blocks, and the purpose-built software created for end applications before the chip is built.

Hardware emulators and desktop FPGA prototype boards are well-known verification tools used for this task, unlike simulation that dominates in the early design stages and whose use is limited to circuit blocks due to performance. Once full-chip verification begins, greater speed is needed to handle the number of tests required to achieve full hardware coverage, and hardware/software with emulation takes on the bulk of the work. In parallel, when register level code (RTL) code reaches stability, validation of software applications may commence using desktop prototyping boards.

Enterprise FPGA prototyping is now being used to fill the gap between an emulator’s powerful analysis/debug capabilities and the raw performance of a desktop FPGA prototyping board. It blends features of emulation and desktop prototyping to address new use cases and offloads emulators. Verification groups can increase their high-speed hardware-based verification resources and optimize total cost of ownership.

Combining emulators, desktop FPGA prototyping boards, and an enterprise FPGA prototyping platform working on the same SoC design ensures thorough and exhaustive verification and validation of hardware and software of a complex SoC.

Emulators provide capacity and debug visibility for verifying large SoCs, including hardware, software drivers, operating systems, and portions of application code.

Enterprise FPGA prototypes provide higher-performance hardware for running emulation regression suites, executing Executing in-circuit emulation (ICE) tests, and verifying application software.

Desktop FPGA prototypes are available to software developers who want more direct contact with their prototypes for local testing. Those tests can move back and forth between the desktop and enterprise units to maximize use of available resources. In addition, developers can ship desktop prototypes to their customers to smooth system integration, verification, and validation.

Emulation tasks

Emulators are workhorses of SoC hardware verification because they execute orders of magnitude faster than simulation and test hardware placed on a single chip. Emulator design reflects a balance between performance, the infrastructure required to implement the range of designs, and the instrumentation that allows thorough debug. While they don’t run as fast as a final application, they are fast enough to boot operating systems, explore low-level software like drivers and bare-metal programs, and run benchmarks and software workloads.

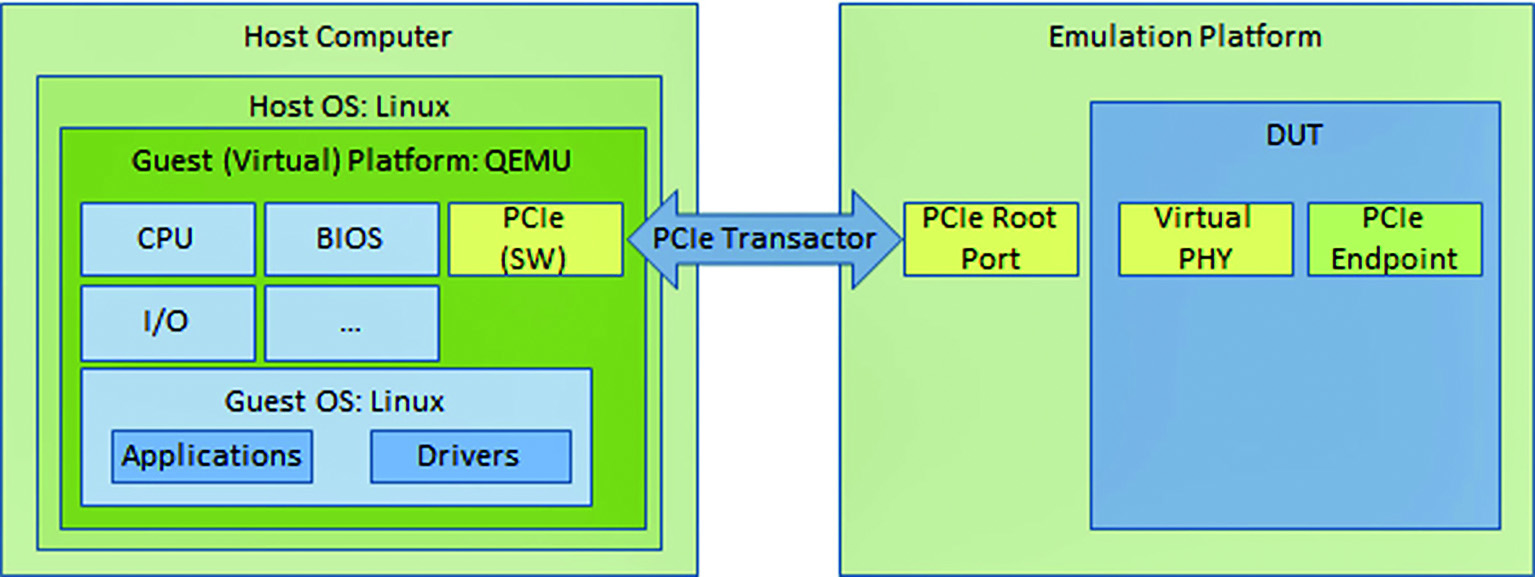

ICE is another emulator task. By connecting the emulator to physical networks or other hardware to deliver realistic data traffic, it is possible to thoroughly exercise the design under test (DUT) with real-world workloads and unearth deep-seated bugs. Because ICE connections required rate adapters to slow down real-world data rates to match the emulator speed, verification groups moved to virtualized traffic generators instead of ICE.

Virtual traffic generators can replace ICE physical target systems without requiring speed rate adapters, facilitating the unmanned deployment of emulators in data centers, accessible remotely 24/7. Virtualized traffic generators can create realistic workloads for a wide range of applications.

Desktop prototype boards

While emulators test out low-level software, they’re not always the best tool for verifying higher-level application software. Such software must be debugged at the software level where fast speed of execution is paramount and hardware debug unnecessary.

Desktop prototype boards are configured once the hardware design has stabilized with few silicon design changes during the remaining verification cycle. The re-configurable FPGA network allows performance to be optimized as the DUT is implemented and run close to an order of magnitude faster than the emulator.

These boards are distributed to software developers who plug them into their desktop servers to run software tests and quickly obtain results based on the actual hardware design. Because of their speed, it has been easier to connect these boards directly to real-world data sources without resorting to speed rate adapters.

Also, the high performance and portability of FPGA prototype boards makes them unique vehicles as demo platforms for OEM providers of IP blocks.

Offloading emulators with an enterprise prototyping platform

The emulator has a central SoC-verification role. In addition to hardware debug and hardware/software integration, it can be used for running long regression test suites. As an example, tests that have already passed must be rerun each time the circuit changes to guarantee the DUT’s integrity. Executing these regression suites quickly is critical to avoid exceeding the allocated time window. The emulator can meet the challenge while its extensive debug capabilities remain unused. Those debug capabilities are used to trace a bug and determine the root cause of the failure only when a regression test fails.

Complementing an emulator with an enterprise prototyping platform maximizes the investment in hardware-assisted technology. The enterprise prototyping platform can be instantiated in the data center like an emulator and accessed for hardware regression use. Rack-mounted and remotely accessible, it performs at a speed closer to a desktop prototype than an emulator, favoring its deployment for running regression suites and off-loading the emulator. If a regression test fails, then debug resources available on the emulator can be used by moving that test back into the emulation environment for root-cause debug.

An enterprise prototype performs five times faster than an emulator. With some additional FPGA network optimization work, that gain can be increased up to 10 times for faster regression without bogging down the emulators. It accommodates larger design sizes than the desktop prototype board and is less costly than the emulators.

Enterprise prototypes can be used for ICE, leveraging direct, unvirtualized data-source connections. While physical data sources used for emulation suffer extra transaction latency due to the network connection, a direct data connection delivers that data closer to real time.

Until recently, a full-SoC verification environment featured the emulator housed in a data center with resources accessed over the network and the desktop prototype board located in software developers’ offices. The combination of emulation, enterprise prototyping, and desktop prototyping bring an SoC to market faster and with greater confidence in the correctness of the silicon while verification groups reduce overall cost of their hardware verification resources.