Why are the analog and digital portions of an IC design so different?

Since the creation of the first transistor, the complexity of integrated circuit (IC) design has increased massively, reflecting the renowned “Moore’s Law” of semiconductor production. Developments in digital design have been a key contributor to this constant expansion. What many people don’t realize is that even in the case of “purely digital” IC designs, such as predominantly digital system-on-chip (SoC) devices, there are going to be some analog elements (e.g., temperature, voltage, and process sensors along with corresponding analog-to-digital converters). How do the digital and analog portions of the design differ? How does analog IP work? And does “silicon-proven” analog IP really mean high-quality IP?

Contemporary digital design

Digital design is initially carried out in a mostly process agnostic manner, with the achievable performance and the likelihood of logic depth serving as major guiding factors. Ease of design portability between process nodes is therefore viable without compromising the verification quality. As the level of design capture abstraction has increased, a thorough design tool flow and verification methodology to evaluate consistency and compliance at each stage of the flow has led to a significant improvement in designer productivity. Together with upgraded verification and signoff tools, this has made it possible to automate the digital design process to produce complex, high-quality ICs that no longer rely on silicon validation for proof.

Even though the digital design is process independent, the deployment of the design from synthesis through place-and-route takes account of the target process node through the various models and signoff procedures. The same design can, in effect, be implemented significantly differently and optimized to benefit from the specific process features.

Digital vs. analog design

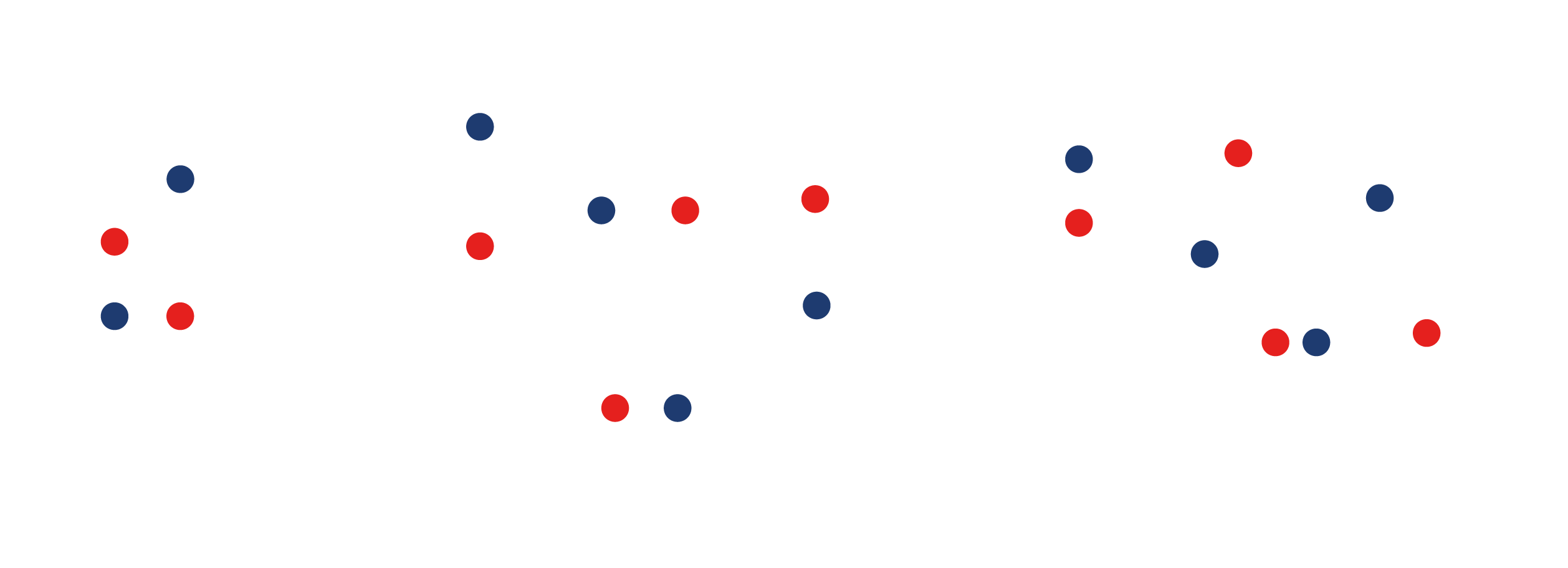

There are some parallels between the analog design flow and the digital design flow—for instance, the analog flow’s “architecture” and the digital flow’s “functional design” are similar, as are the analog flow’s “layout” and digital flow’s “place-and-route.” However, there are also clear differences between the two.

First, unlike the “linear” digital design flow, the analog design flow involves circular iterations across multiple cycles. The design flow will iterate several times in the analog design flow loop, often between the layout and post-sim stages. This depends on the complexity of the analog circuit block, the circuit designer’s experience, knowledge of the technology node, and many other considerations. In some circumstances, the architecture chosen cannot fulfil the circuit specifications. This results in a restart from the beginning. The time and effort required to complete an analog circuit are, to put it plainly, approximations. The uncertainty grows as the complexity rises or there are changes in technology.

Next, the technology or process node of an analog IP is determined at the outset of the design, and the available devices for architecture exploration and design, model cards for simulation, layout rules, and the metal R-C models are all process specific. The entire analog design often needs to be started again from scratch if a project manager decides to select a process node or even adjust the existing node’s process options.

Finally, there is very little CAD automation in analog design. Even though there are excellent EDA tools, different analog blocks have different design methods. Also, layout is custom, and simulations are circuit-, process-, and application-dependent.

What makes high-quality analog IP?

The first step is to select a solid circuit architecture that is stable, robust, and suitable for mass production. Up to date process design kits (PDKs) from foundries offer models for the front-end (transistors, varactors, diodes, etc.) and back-end (resistors, capacitors, metals, etc.) for simulations, as well as a variety of command files for DRC, LVS, and parasitic extraction. Today, the major foundries provide PDKs that have very good correlation between model and physical silicon. All that is required is a proper PDK installation and selecting the process option.

Thorough behavioral simulation and circuit simulations at the crucial process, voltage, and temperature (PVT) corners are needed to ensure the circuit will function as expected. Circuit layout involves knowledge of the circuit design and a clear understanding of how the process impacts on analog performance. This requires a skilled group of layout engineers and circuit designers with broad expertise.

With a solid circuit architecture, accurate PDK, thorough simulations, detailed layout, and an experienced team, a high-quality analog IP will be delivered with fewer rounds of iterations. Traditionally, however, analog designers have been hard to find, and high-quality analog IP is expensive.

What is “silicon-proven” IP?

An issue that IC design companies often raise is whether a particular analog IP is “silicon proven” or requiring an analog IP to be “silicon proven” to be qualified for use. The general definition of a “silicon-proven” IP is an IP that has been manufactured on silicon and has had its functionality bench-test measured; hence, verified “on-silicon.” Once an IP is “silicon-proven,” it gains credibility that it will work as expected on a production chip with the identical layout on the same process technology. However, this silicon proof is based only on a sample as validation of the design is usually measured at specific points.

Whether this “silicon proven” IP is “production quality” is determined before the manufacturing of the IP. This means the architecture chosen, the comprehensive simulations and design corners covered, the diligence put into the layout, and the effort in verification during development. In other words, an IP that is “silicon-proven” is merely a sanity check, only proving that the IP development flow “seems” to be “okay,” which really is not sufficient proof of quality.

Some “silicon-proven” IPs come from production chips and have withstood a variety of real-world, high-volume tests. These IPs can be credible in terms of their quality but are designed specifically for a certain product at a particular process node. Process-porting is necessary for a project in a different node, thereby removing the IP from the category of “silicon-proven.” It may be possible to modify silicon-tested IPs, but the extra cost ($xxx k) and time (6 months to a year) is likely to be too much to justify. The original IP’s “silicon-proven” status is also revoked by modifications.

In summary

Even in predominantly digital ICs, analog design and analog IP have an important role to play. Despite claims about an analog IP being “silicon-proven,” the quality of that analog IP is actually determined by the use of a solid architecture, accurate PDK, thorough simulations, and an experienced design team. All these factors are embodied by Agile Analog’s innovative analog IP technology.